Задание на курсовую работу по курсу «Схемотехника»

Тема: Проектирование цифровых устройств с использованием пакета VHDL

Срок представления к защите: 13 мая 2005г.

Задание выдано 5

марта 2005г.

Задание принято к исполнению __________ /студент гр.246 Е.С./

Задание выдал __________ /асс. каф. САПР ВС /

Содержание :

Задание………………………………………………………………………………………………………….2

1. Введение…………………………………………………………………………………………………….4

2. Краткое описание схемы…………………………………………………………………………….5

3. Моделирование элементов схемы……………………………………..…………6

3.1. Описание элемента К133ЛН1……………..

……………………………………………………6

3.2. Описание элемента К133ИЕ5

…………………………………………………………………..8

3.3. Описание элемента К133ТМ2

…………………………………………………………………11

3.4. Описание элемента К133ИД4 ……………………………………………………………14

3.5. Описание элемента К133ЛА3………………………………………………………………….16

3.6. Описание элемента К133ИР13………………………………………………………………..18

3.7. Описание элемента

К514ИД1………………………………………………………………….21

3.8. Описание элемента

К133ЛП5………………………………………………………………….24

4. Моделирование схемы…………………………………………………………..26

5.Заключение………………………………………………………………………………………………..31

Список

литературы……………………………………………………………………………………….32

1. Введение

Современный мир уже нельзя представить без цифровых

устройств. С каждым годом цифровая техника становится все сложнее,

функциональней, производительной, но при этом габариты микросхем как правило

меньше по сравнению с предыдущими моделями, это достигается благодаря высокой

степени интеграции, когда на небольшом кристалле размещают до 1011

элементов. Поэтому в настоящее время для разработки интегральных микросхем

используют специальные программные продукты, называемые языками описания

аппаратуры (ЯОА). Одним из наиболее распространенных ЯОА является VHDL. С

помощью этого языка разрабатываются БИС, СБИС и ПЛИС, которые являются базовыми

элементами современных цифровых устройств. Возможности данного языка позволяют

моделировать как отдельные простейшие элементы, такие как триггеры, счетчики,

регистры, так и сложнейшие микросхемы, содержащие сотни и тысячи различных

элементов, что делает VHDL основным инструментом разработчика таких

схем.

2. Краткое описание схемы

Данная схема является частью сигнатурного

сигнализатора, который позволяет локализовать неисправности с точностью до

элемента в отдельных цифровых блоках элементов и в сложных цифровых системах,

включая микропроцессоры.

Сигнатурный

анализатор (СА) состоит из собственно анализатора (рис.1), который будет описан в данной работе,

и формирователя тестовых воздействий. СА функционально содержит три узла: сдвиговый

регистр с обратными связями (DD7, DD8, DD13), узел управления (DD1…DD6) и

узел индикации (DD9…DD12, HG1…HG4).

Основа СА

– сдвиговый регистр с обратными связями, выполненный на двух 8-разрядных

универсальных сдвиговых регистрах DD7, DD8. Обрабатываемая двоичная последовательность

суммируется по модулю 2 в сумматоре DD13 с разрядами обратной связи сдвигового

регистра (разряды 7, 9, 12, 16) и подаётся на вход сдвигового регистра.

Информация сдвигается вправо по фронту синхросигналов, приходящих из узла

управления на входы С сдвиговых регистров DD7, DD8.

Узел управления вырабатывает сигналы начальной установки и

синхроимпульсы для сдвиговых регистров СА и формирователя тестовых воздействий.

В узел управления входят генератор импульсов на DD1.1…DD1.3,

распределитель импульсов на DD2, DD4, триггер сброса на DD5.1, DD5.2 и

триггеры DD3.1, DD3.2, DD6.1, формирующие измерительный интервал для

обработки входной двоичной последовательности.

Узел

индикации создан из четырёх дешифраторов DD9…DD12 и 7-сегментных индикаторов HG1…HG4.

Рис.1.

Схема сигнатурного анализатора.

3. Моделирование элементов схемы

3.1. Микросхема К133ЛН1

Логический

элемент НЕ серии ТТЛ К133ЛН1 выполняет логическую функцию НЕ.

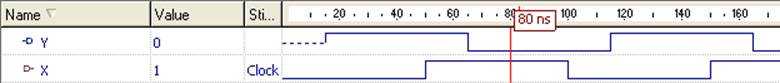

Рис. 2. Элемент НЕ.

Логическая функция элемента: Y = X.

Таблица

1. Значения функции НЕ.

|

Y |

|

|

Н |

В |

|

В |

Н |

Текст моделирующей программы.

Обозначение

портов показано на рис. 2, вейвформы на рис. 3.

— File: K133LN1.vhd

— created by Design Wizard:

04/17/05 16:31:07

-library IEEE;

use IEEE.std_logic_1164.all;

entity K133LN1

is

port (

X: in STD_LOGIC;

Y: out STD_LOGIC

);

end K133LN1;

architecture K133LN1 of

K133LN1 is

begin

process(x)

begin

y<=not x after 18 ns;

end process;

end K133LN1;

Рис.3. Работа элемента НЕ

3.2.

Микросхема К133ИЕ5

Микросхема К133ИЕ5 является четырехзарядным,

асинхронным счетчиком пульсаций. Его обозначение показано на рис. 2. Режим

работы соответствует таблице 2. Если микросхема К133ИЕ5 применяется как

счетчик-делитель на 16, необходимо соединить выводы 1 и 12. При этом

последовательность счета от 0 до 15 ( т.е. последовательность смены логических

уровней на выходах Q0 – Q3) будет соответствовать таблице 3.

Таблица

2. Режим работы счетчика К133ИЕ5.

|

Вход сброса |

Выход |

||||

|

R1 |

R2 |

Q0 |

Q1 |

Q2 |

Q3 |

|

B H B H |

B B H H |

H |

H |

H |

H |

|

Счет |

Таблица

3. Последовательность счета К133ИЕ5.

|

Счет |

Выход |

Счет |

Выход |

||||||

|

Q0 |

Q1 |

Q2 |

Q3 |

Q0 |

Q1 |

Q2 |

Q3 |

||

|

1 2 3 4 5 6 7 |

H B H B H B H B |

H H B B H H B B |

H H H H B B B B |

H H H H H H H H |

8 9 10 11 12 13 14 15 |

H B H B H B H B |

H H B B H H B B |

H H H H B B B B |

B B B B B B B B |

Рис. 4.

Обозначение счетчика К133ИЕ5.

Текст

моделирующей программы.

Обозначение

портов показано на рис. 4, вейвформы на рис. 5, 6

— File: K133IE5.vhd

— created by Design Wizard:

04/27/05 13:00:34

-library IEEE;

use IEEE.std_logic_1164.all;

use

IEEE.std_logic_unsigned.all;

entity counter is

port (

C2: in STD_LOGIC;

R0: in STD_LOGIC;

R1: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR

(3 downto 0)

);

end counter;

architecture K133IE5of K133IE5

is

begin

process(C2,R0,R1) is

variable X:

STD_LOGIC_VECTOR (3 downto 0):=»0000″;

begin

if R0=’1′ and R1=’1′ then

Q<=transport

«0000» after 26 ns;

elsif C2=’0′ and

C2’DELAYED=’1′ and X<15 then

X:=X+1;

end if;

Q<=transport X after

26 ns;

end process;

end K133IE5;

Рис. 5.

Сброс счетчика К133ИЕ5.

Рис. 6.

Счетчик К133ИЕ5 в режиме счета.

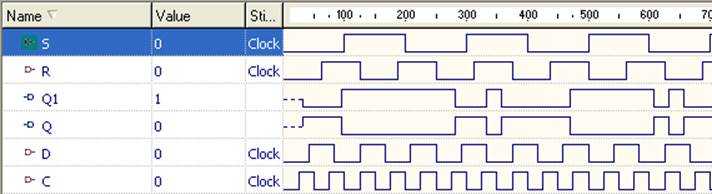

3.3. Микросхема К133ТМ2

Рис.7.

Обозначение триггера К133ТМ2.

Микросхема К133ТМ2 серии ТТЛ содержит два

независимых D-триггера. У каждого триггера есть входы R,D, C,S , а

также выходы Q, Q. Логика работы микросхемы показана в таблице.

Таблица 4. Состояния триггера К155ТМ2.

|

Режим работы |

вход |

выход |

||||

|

S |

R |

C |

D |

Q |

Q |

|

|

установка |

Н |

В |

X |

X |

В |

Н |

|

сброс |

В |

Н |

X |

X |

Н |

В |

|

Неопределён- ность |

Н |

Н |

X |

X |

В |

В |

|

Загрузка 1 |

В |

В |

В |

В |

Н |

|

|

Загрузка 0 |

В |

В |

Н |

Н |

В |

Текст моделирующей программы программы.

Обозначение

портов показано на рис. 7, вейвформы на рис. 8.

—

File: K133TM2.vhd

—

created by Design Wizard: 04/17/05 17:11:23

-library

IEEE;

use

IEEE.std_logic_1164.all;

entity

K133TM2 is

port (

S: in STD_LOGIC;

C: in STD_LOGIC;

D: in STD_LOGIC;

R: in STD_LOGIC;

Q: out STD_LOGIC;

Q1:out STD_LOGIC

);

end

K133TM2;

architecture

K133TM2 of K133TM2 is

begin

process

(s,r,c,d)

variable

q0,a: std_logic;

begin

a:=’1′;

if

R=’1’and S=’0′ and (C=’1′ or C=’0′)and (D=’1′ or D=’0′)then q0:=’0′;

else

if

R=’0′ and S=’1′ and (C=’1′ or C=’0′)and (D=’1′ or D=’0′) then q0:=’0′;

else

If

R=’1′ and S=’1′ then

if C’event and C=’1′ and D=’1′ then q0:=’1′;

else

if C’event and C=’1′ and D=’0′ then q0:=’0′;

end if;

end if;

else

if

R=’0′ and S=’0’and(C=’1′ or C=’0′)and (D=’1′ or D=’0′) then q0:=a;

end

if;

end

if;

end

if;

end

if;

q

<= q0 after 32 ns;

a

:= q0;

q1<=not(q0)

after 32 ns;

end

process;

end

K133TM2;

Рис.8. Работа

триггера К133ТМ2