4.3.Файл IC_k155tm2.VHD

——————————————————————-

— File: ..\SRC\IC_k155tm2.VHD

——————————————————————-

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k155tm2 is

port

Sin: in STD_LOGIC;

Din: in STD_LOGIC;

Cin: in STD_LOGIC;

Rin: in STD_LOGIC;

Q: inout STD_LOGIC;

Q_inv: out STD_LOGIC

);

end IC_k155tm2;

architecture IC_k155tm2 of IC_k155tm2 is

signal Qt:STD_LOGIC;

begin

process (Rin, Sin, Cin)

begin

Qt<= Q;

if (Rin=’0′ and Sin=’1′) then Qt <=

‘0’;

elsif (Rin=’1′ and Sin=’0′) then Qt <=

‘1’;

elsif (Rin=’1′ and Sin=’1′) then

if(Cin’event and Cin=’1′) then

if(Din=’1′)

then Qt <= ‘1’;

else Qt <= ‘0’;

end if;

end if;

else

assert not (Sin=’0′ and Rin=’0′)

report «одновременный 0 на S и R входе

D-триггера»

severity warning;

end if;

Q <= transport Qt after 40 ns;

Q_inv <= transport not Qt after 40 ns;

end process;

end IC_k155tm2;

4.6.Файл Top.vhd

——————————————————————-

— File: ..\SRC\Top.VHD

——————————————————————-

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity Top is

port

In1: inout STD_LOGIC;

In2: inout STD_LOGIC;

A0: in STD_LOGIC;

A1: in STD_LOGIC;

OBB: in STD_LOGIC;

Read: in STD_LOGIC;

Write: in STD_LOGIC;

At: out STD_LOGIC;

Ct: out STD_LOGIC;

Dt: out STD_LOGIC;

TPR: out STD_LOGIC;

D: out STD_LOGIC_VECTOR (11 downto 0)

);

end Top;

architecture Structure of Top is

component N_AND is

port

a: in STD_LOGIC;

b: in STD_LOGIC;

c: out STD_LOGIC

);

end component;

component k155ie5 is

port

CLK: in STD_LOGIC;

RESET: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR (3 downto 0)

);

end component;

component k155tm2 is

port

Sin: in STD_LOGIC;

Din: in STD_LOGIC;

Cin: in STD_LOGIC;

Rin: in STD_LOGIC;

Q: inout STD_LOGIC;

Q_inv: out STD_LOGIC

);

end component;

component k589ir12 is

port

DAin: in STD_LOGIC_VECTOR(7 downto 0);

R: in STD_LOGIC;

BM1: in STD_LOGIC;

BM2: in STD_LOGIC;

CT: in STD_LOGIC;

BP: in STD_LOGIC;

QAout:out STD_LOGIC_VECTOR(7 downto 0);

INR: out STD_LOGIC

);

end component;

component k155id4 is

port

A0: in STD_LOGIC;

A1: in STD_LOGIC;

D1: in STD_LOGIC;

D2: in STD_LOGIC;

C1: in STD_LOGIC;

C2: in STD_LOGIC;

Q0: out STD_LOGIC_VECTOR (3 downto 0);

Q1: out STD_LOGIC_VECTOR (3 downto 0)

);

end component;

signal a_bus:STD_LOGIC_VECTOR (16 downto 1);

signal s1, s2, s3, s4, s5, s6, s7, s8, s9, s10,

s11, s12, s13, s14, s15:STD_LOGIC;

signal grn, one:STD_LOGIC;

signal s12_out, s18_Q0_out, s18_Q1_out:STD_LOGIC_VECTOR(3 downto

4.2.Файл IC_k155ie5.vhd

——————————————————————-

— File: ..\SRC\IC_k155ie5.vhd

——————————————————————-

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k155ie5 is

port

CLK: in STD_LOGIC;

RESET: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR (3 downto 0)

);

end IC_k155ie5;

architecture IC_k155ie5 of IC_k155ie5 is

begin

process (CLK, RESET)

variable Qint: STD_LOGIC_VECTOR (3 downto 0);

begin

if RESET=’1′ then

Qint := «0000»;

else

if CLK’event and CLK=’1′ then

if Qint<15 then

Qint:=Qint+1;

else

Qint:=»0000″;

end if;

end if;

end if;

Q <= transport Qint after 135 ns;

end process;

end IC_k155ie5;

4.5.Файл IC_k589ir12.vhd

——————————————————————-

— File: ..\SRC\IC_k155ir12.vhd

——————————————————————-

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k589ir12 is

port

DAin: in STD_LOGIC_VECTOR(7 downto 0);

R: in STD_LOGIC;

BM1: in STD_LOGIC;

BM2: in STD_LOGIC;

CT: in STD_LOGIC;

BP: in STD_LOGIC;

QAout:out STD_LOGIC_VECTOR(7 downto

0):=»00000000″;

INR: out STD_LOGIC:=’0′

);

end IC_k589ir12;

architecture IC_k589ir12 of IC_k589ir12 is

signal Regist:STD_LOGIC_VECTOR(7 downto

0):=»00000000″;

begin

process(R, BM1, BM2, CT, BP)

begin

if R’event and R=’0’then

QAout <= «00000000»;

else

if (CT and not BM1 and BM2) =’1′ then

QAout <= transport DAin after 30 ns;

else

QAout <= transport «00000000» after

30 ns;

end if;

end if;

end process;

end IC_k589ir12;

Аналоги микросхем серии 589- 599, 710- 740

Категория

Функциональное назначение и зарубежные аналоги микросхем отечественного производства серии 589- 599 и 710- 740

| Тип/Серия | Аналог | Производитель аналога | Назначение |

| 589АП16 | 8216 | INTEL | Шинный формирователь |

| 589АП26 | 8226 | INTEL | Шинный формирователь с инверсией |

| 589ИК01 | 3001 | INTEL | Блок микропрограммного управления |

| 589ИК02 | 3002 | INTEL | Центральный процессорный элемент |

| 589ИК03 | 3003 | INTEL | Схема ускоренного переноса. |

| 589ИК12 | 8212 | INTEL | Многорежимный буферный регистр. |

| 589ИК14 | 8214 | INTEL | Схема приоритетного прерывания. |

| 589ИР12 | 8212 | INTEL | Многорежимный буферный регистр. |

| 589РА04 | 3104 | INTEL | Ассоциативное ЗУ (4 х 4). |

| 589РУ01 | 3101А | INTEL | Статическое ОЗУ (16 x 4). |

| 589ХЛ4 | Многофункциональное устройство синхронизации. | ||

| 590ИР1 | MТ8571, MI-6-8572 | MITEL | Десятичный статический регистр (10 р, КМОП) |

| 590КН1 | 3708 | FAIRCHILD | 8-и канальный аналоговый коммутатор (р-МОП) |

| 590КН2 | HI-1800 | HARRIS | Четыре ключа со схемой управления (КМОП) |

| 590КН3 | HI-509A | HARRIS | 8-и канальный аналоговый коммутатор (4 х 2, КМОП) |

| 590КН4 | HI-303 (IH-5043, AD7512) | HARRIS (INTERSIL, AD) | Четыре ключа со схемой управления (КМОП) |

| 590КН5 | HI-201-2 (DG201, IH5201) | HARRIS | Четыре ключа со схемой управления (однополюсный, КМОП). |

| 590КН6 | HI-508A | HARRIS | 8-и канальный аналоговый коммутатор (КМОП). |

| 590КН7 | HI-5048 (HI5046A) | HARRIS | Четыре ключа со схемой управления (двухполюсный, КМОП). |

| 590КН8 | SD5000 (SD5002, SD5200) | SILICONIX | Четыре ключа с повышенным быстродействием (КМОП). |

| 590КН9 | IH5151, HI5048A, HI5051, HI400 | INTERSIL, HARRIS | Два низкоомных ключа со схемой управления (КМОП) |

| 590КН10 | DG202, HI201H, IH5201 | SILICONIX | Четыре ключа с малым уровнем помех (КМОП) |

| 590КН11 | DG509 (MVD807M) | SILICONIX | Четырехканальный коммутатор со схемой управления (КМОП) |

| 590КН12 | DG221, AD7591DJ | SILICONIX, AD | Четыре ключа с памятью (КМОП) |

| 590КН13 | HI-201 (HI401, HI506-2) | HARRIS | Четыре ключа со схемой управления (однополюсный, КМОП) |

| 590КН14 | CD22100 | RCA | Матричный коммутатор (4 x 4, КМОП) |

| 590КН15 | AD7591 | AD | Четыре быстродействующих ключа со схемой управления (КМОП) |

| 590КН17 | HI-524 | HARRIS | Четырехканальный видеокоммутатор со схемой управления (КМОП) |

| 590КН19 | HI-508A | HARRIS | 8-и канальный аналоговый коммутатор (КМОП) |

| 590КН20 | ~HI-509A | Два 4-х канальных коммутатора с памятью (КМОП) | |

| 590КН21 | MТ8809 | MITEL | Матричный коммутатор (8 x 8, КМОП) |

| 590КН22 | MAX316 | MAXIM | 10-и канальный видеокоммутатор (КМОП) |

| 590КН23 | б/а | 8-и канальный аналоговый коммутатор со схемой управления (4 х 2,КМОП) | |

| 590КН24 | Видеокоммутатор (10 x 1, КМОП) | ||

| 590КН25 | б/а | Два ключа со схемой управления (КМОП) | |

| 590КН26 | б/а | Восьмиканальный аналоговый коммутатор (КМОП) | |

| 590КН27 | MТ8816 | MITEL | Матричный коммутатор (8 х 16, КМОП) |

| 590КТ1 | AD7519 | AD | Четыре переключателя со схемой управления (КМОП) |

| 591КН1 | IH5116 (MI-6-8752) | INTERSIL | 16-и канальный аналоговый коммутатор с произвольным выбором канала (р-МОП) |

| 591КН2 | HI-507 | HARRIS | 16-и канальный аналоговый коммутатор с дешифратором (8 x 2, КМОП) |

| 591КН3 | HI-506 | HARRIS | 16-и канальный аналоговый коммутатор со схемой управления (КМОП) |

| 591КН4 | CD22102 | RCA | Матричный коммутатор (2 х (4 х 4), КМОП) |

| 591КН5 | Матричный коммутатор (8 x 8, КМОП) | ||

| 592ГФ1 | |||

| 592КТ1 | Четырехканальный коммутатор на p-МОП транзисторах | ||

| 592ПУ1 | |||

| 592ПУ2 | |||

| 593БР1 | TAD32 | RETICON | Активная схема задержки на ПЗС |

| 594КТ1 | AD554 | AD | Четыре токовых ключа с повышенным быстродействием |

| 594ПА1 | AD562 | AD | ЦАП (12р) |

| 596РЕ1 | MKB36000-84 | MOSTEK | ПЗУ (8k х 8, бипол.) |

| 596РЕ2 | uPD73100 | NEC | ПЗУ (64k х 16, бипол.) |

| 597СА1 | Am685 (Am695) | AMD | Стробируемый компаратор (ЭСЛ) |

| 597СА2 | Am686 | AMD | Стробируемый компаратор (ТТЛ) |

| 597СА3 | ICL8001 (LM119 ) | INTERSIL | Два компаратора |

| 597СА4 | VC7695 | VTC | Стробируемый компаратор (ХЛ) |

| 599ЛД1 | б/а | Два расширителя по ИЛИ | |

| 599ЛК1 | б/а | Логический элемент 4-4И-2ИЛИ-НЕ/4-4И-2ИЛИ с расширением по ИЛИ | |

| 599ЛК3 | б/а | Два логических элемента 2-2-2ИЛИ-НЕ/2-2-2ИЛИ | |

| 599ЛК4 | б/а | Логический элемент 2-2-2-2И-4ИЛИ-НЕ/2-2-2-2И-4ИЛИ с расширением по ИЛИ | |

| 599ЛК5 | б/а | Логический элемент 8И-НЕ/8И с расширением по ИЛИ | |

| 599ЛК6 | б/а | Два логических элемента 2-2И-2ИЛИ-НЕ/2-2И-2ИЛИ | |

| 599ЛК7 | б/а | Логический элемент 2-2-2-2И-4ИЛИ-НЕ/2-2-2-2И-4ИЛИ с расширением по ИЛИ | |

| 599ЛП1 | б/а | Два приемника сигналов с парафазным входом и выходом | |

| 710УД1 | ОУ | ||

| 722ТЛ1 | б/а | Триггер Шмитта | |

| 722УД1 | MC1325 | MOTOROLA | Двухкаскадный дифференциальный УПТ |

| 722УН1 | MC101 | MOTOROLA | Двухкаскадный УПТ |

| 722УН2 | 2А-30 | FERRANTI | Каскодный усилитель |

| 722УП1 | б/а | Видеоусилитель | |

| 743КТ1 | SN75614 | TI | Прерыватель сигналов |

| 740УД1 | uA702 | FAIRCHILD | ОУ широкого применения |

| 740УД2 | ~CA3033 (~uA723) | RCA | ОУ широкого применения |

| 740УД3 | ОУ широкого применения | ||

| 740УД4 | ОУ широкого применения | ||

| 740УД5 | ~CA3015 | RCA | ОУ широкого применения |

4.4.Файл IC_k155id4.vhd

——————————————————————-

— File: ..\SRC\IC_k155id4.vhd

——————————————————————-

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k155id4 is

port

A0: in STD_LOGIC;

A1: in STD_LOGIC;

D1: in STD_LOGIC;

D2: in STD_LOGIC;

C1: in STD_LOGIC;

C2: in STD_LOGIC;

Q0: out STD_LOGIC_VECTOR (3 downto 0);

Q1: out STD_LOGIC_VECTOR (3 downto 0)

);

end IC_k155id4;

architecture IC_k155id4 of IC_k155id4 is

signal Qres0:STD_LOGIC_VECTOR (3 downto 0);

signal Qres1:STD_LOGIC_VECTOR (3 downto 0);

begin

Qres0 <=

«0111» when (A0 & A1 & D2 &

D1)=»0001″ else

«1011» when (A0 & A1 & D2 &

D1)=»0101″ else

«1101» when (A0 & A1 & D2 &

D1)=»1001″ else

«1110» when (A0 & A1 & D2 &

D1)=»1101″ else

«1111»;

Qres1 <=

«0111» when (A0 & A1 & C1 &

C2)=»0011″ else

«1011» when (A0 & A1 & C1 &

C2)=»0111″ else

«1101» when (A0 & A1 & C1 &

C2)=»1011″ else

«1110» when (A0 & A1 & C1 &

C2)=»1111″ else

«1111»;

Q0 <= transport Qres0 after 32 ns;

Q1 <= transport Qres1 after 32 ns;

end IC_k155id4;

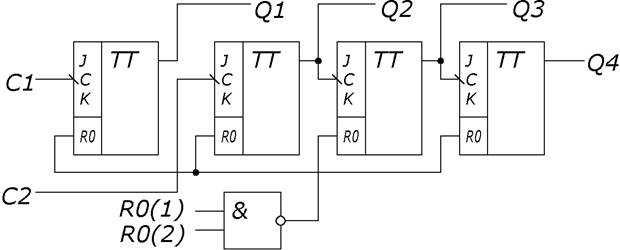

3.2. Микросхема К155ИЕ5

Микросхема представляет собой четырехразрядный

двоичный асинхронный счетчик.

Микросхема счетчика состоит из четырёх JK-триггеров,

которые соединены

соответствующим образом (Рис.5) для образования счетчика

делителя на 2 и 8.

Рис.4. Условное графическое обозначение

К155ИЕ5

Рис.5. Функциональная схема К155ИЕ5

Назначение выводов

|

Вывод |

Назначение |

Вывод |

Назначение |

|

|

1 |

Вход счетный С2 |

8 |

Выход Q3 |

|

|

2 |

Вход установки в 0 R0(1) |

9 |

Выход Q2 |

|

|

3 |

Вход установки в 0 R0(2) |

10 |

Общий |

|

|

4 |

Свободный |

11 |

Выход Q4 |

|

|

5 |

Напряжение питания |

12 |

Выход Q1 |

|

|

6 |

Свободный |

13 |

Свободный |

|

|

7 |

Свободный |

14 |

Вход счетный С1 |

Время задержки распространения 135 нс.

У счетчика имеются лишь входы сброса в нуль. Счетчик

работает по заднему фронту положительного входного сигнала. Выделены две

части: один триггер (одноразрядный счетчик) со входом С1 и выходом 1 и три

триггера (трехразрядный счетчик) со входом С2 и выходами 2, 4, 8. Оба

счетчика двоичные, то есть первый считает до двух, а второй — до 8. При

объединении входа С2 с выходом 1 получается 4-разрядный двоичный счетчик,

считающий до 16. Счет производится по отрицательному фронту входного сигнала.

Предусмотрена возможность сброса в нуль по сигналам R1 и R2, объединенных

функцией И.

Таблица истинности счетчика ИЕ5 присоединении входа С2 и

выхода 1 (при 4-разрядном выходном коде):

|

Входы |

Выходы |

|||||

|

С1 |

R1 |

R2 |

8 |

4 |

2 |

1 |

|

Х |

1 |

1 |

||||

|

1→0 |

Х |

Счет |

||||

|

1→0 |

Х |

Счет |

Счет производится согласно следующей

таблице:

|

Счет |

Выход |

|||

|

8 |

4 |

2 |

1 |

|

|

1 |

1 |

|||

|

2 |

1 |

|||

|

3 |

1 |

1 |

||

|

4 |

1 |

|||

|

5 |

1 |

1 |

||

|

6 |

1 |

1 |

||

|

7 |

1 |

1 |

1 |

|

|

8 |

1 |

|||

|

9 |

1 |

1 |

||

|

10 |

1 |

1 |

||

|

11 |

1 |

1 |

1 |

|

|

12 |

1 |

1 |

||

|

13 |

1 |

1 |

1 |

|

|

14 |

1 |

1 |

1 |

|

|

15 |

1 |

1 |

1 |

1 |

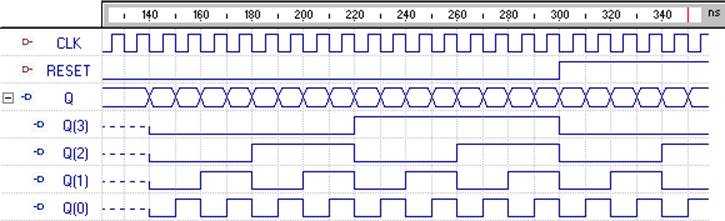

Рис.6. WaveForm К155ИЕ5

Ввод-вывод

Клавиатура

Клавиатура в оригинале — матрица 8х8 кнопок плюс три независимые кнопки, подключенные к контроллеру ввода-вывода D20.

Соответствие битов портов A (PAx) и B (PBx) контроллера D20 кнопкам в матрице

| PA0 | PA1 | PA2 | PA3 | PA4 | PA5 | PA6 | PA7 | |

| PB0 | Home | Таб | 8 ( | @ Ю | H Х | P П | X Ь | |

| PB1 | Стр (Clear) | ПС (Linefeed) | 1 ! | 9 ) | A А | I И | Q Я | Y Ы |

| PB2 | АР2 (Esc) | ВК (Return) | 2 « | : * | B Б | J Й | R Р | Z З |

| PB3 | F1 | ЗБ (Backspace) | 3 # | ; + | C Ц | K К | S С | [ Ш |

| PB4 | F2 | Влево | 4 $ | , < | D Д | L Л | T Т | \ Э |

| PB5 | F3 | Вверх | 5 % | — = | E Е | M М | U У | ] Щ |

| PB6 | F4 | Вправо | 6 & | . > | F Ф | N Н | V Ж | ^ Ч |

| PB7 | (нет кнопки) | Вниз | 7 ‘ | / ? | G Г | O О | W В | (пробел) |

Кнопка УС (Ctrl) подключена к PC6, СС (Shift) — к PC5, Рус/Lat — к PC7 контроллера D20.

Дисплей

В качестве дисплея используется телевизор.

За формирование видеосигнала отвечает контроллер дисплея. Монитор при включении и после сброса настраивает контроллер дисплея на отображение 30 строк по 78 символов (столбцов) в каждой. Не все строки и столбцы попадают в видимую на экране телевизора область, поэтому часть строк и столбцов по краям экрана не используется. На экране отображается область памяти, задаваемая настройками контроллера ПДП. Монитор настраивает ПДП на отображение области памяти, начинающейся с адреса 77C0h.

Магнитофон

Предусмотрена возможность записи блока данных на магнитофон и чтения с него. Сигнал для магнитофона формируется при записи и декодируется при чтении программно, используется манчестерское кодирование. Скорость чтения и записи — около 1200 бит в секунду. Формат блока на магнитной ленте следующий:

| Элемент | Размер, байт |

| Ракорд (нулевые байты) | 256 |

| Синхробайт (E6h) | 1 |

| Начальный адрес в ОЗУ | 2 |

| Конечный адрес в ОЗУ | 2 |

| Данные | (конечный адрес — начальный адрес + 1) |

| Ракорд (нулевые байты) | 2 |

| Синхробайт (E6h) | 1 |

| Контрольная сумма | 2 |

![Radio86rk [licensed for non-commercial use only] / оригинальная разработка](http://dnamemory.ru/wp-content/uploads/9/5/b/95b75f90b1febd1b8a8bfee60b78f5a4.jpeg)

![Radio86rk [licensed for non-commercial use only] / оригинальная разработка](http://dnamemory.ru/wp-content/uploads/5/6/0/560a84d64dc920f99befb94f6b95f226.jpeg)

![Radio86rk [licensed for non-commercial use only] / оригинальная разработка](http://dnamemory.ru/wp-content/uploads/8/3/0/8308accfa2a4b55b4ffc9558f1d21645.jpeg)

![Radio86rk [licensed for non-commercial use only] / оригинальная разработка](http://dnamemory.ru/wp-content/uploads/e/b/1/eb15096db6ac9972a0581fd645881f8b.jpeg)

![Radio86rk [licensed for non-commercial use only] / оригинальная разработка](http://dnamemory.ru/wp-content/uploads/2/3/e/23e1c5462c05ac37de53fcc15f58da4a.jpeg)